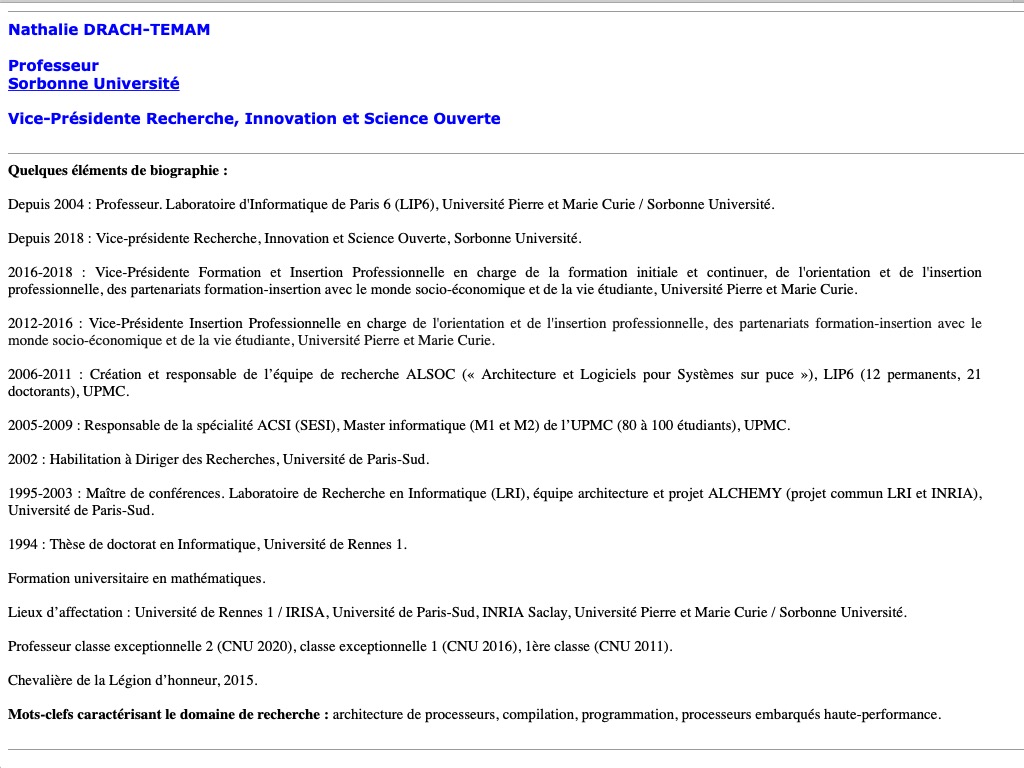

DRACH-TEMAM Nathalie

Professeure

ProfesseureÉquipe : ALSOC

- Sorbonne Université - LIP6

Boîte courrier 169

Couloir 24-25, Étage 4, Bureau 408

4 place Jussieu

75252 PARIS CEDEX 05

01 44 27 20 38

Nathalie.Drach-Temam (at) nulllip6.fr

https://perso.lip6.fr/Nathalie.Drach-Temam/

Six docteurs (2007 - 2015) à Sorbonne Université

- 2015

- DREBES Andi : Parallélisation adaptative pour les applications embarquées haute-performance.

- 2012

- GAMOUDI Oussama : Optimisation adaptative appliquée au préchargement de données.

- 2011

- OZAKTAS Haluk : Compression de code et optimisation multicritère des systèmes embarqués dans un contexte temps réel strict.

- NGUYEN Minh Huu : Sécurisation de processeurs vis-à-vis des attaques par faute et par analyse de la consommation.

- 2010

- ROSIÈRE Mathieu : MORPHEO : Processeur ouvert, haute performance, paramétrable et pérenne pour plate-forme de confiance.

- 2007

- COVELIERS Alexandre : Sensibilité aux jeux de données de la compilation itérative.

Publications 2004-2016

-

2016

- A. Drebes, A. Pop, K. Heydemann, A. Cohen, N. Drach : “Scalable Task Parallelism for NUMA: A Uniform Abstraction for Coordinated Scheduling and Memory Management”, PACT'16 - ACM/IEEE Conference on Parallel Architectures and Compilation Techniques, Haifa, Israel, pp. 125-137 (2016)

- A. Drebes, A. Pop, K. Heydemann, N. Drach, A. Cohen : “NUMA-aware scheduling and memory allocation for data-flow task-parallel applications”, ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, Barcelona, Spain, pp. 44:1-44:2, (ACM New York, NY, USA) (2016)

-

2015

- A. Drebes, K. Heydemann, A. Pop, A. Cohen, N. Drach : “Automatic Detection of Performance Anomalies in Task-Parallel Programs”, 1st Workshop on Resource Awareness and Adaptivity in Multi-Core Computing (Racing 2014), Paderborn, Germany (2015)

-

2014

- A. Drebes, K. Heydemann, N. Drach, A. Pop, A. Cohen : “Topology-Aware and Dependence-Aware Scheduling and Memory Allocation for Task-Parallel Languages”, ACM Transactions on Architecture and Code Optimization, vol. 11 (3), pp. 30, (Association for Computing Machinery) (2014)

- A. Drebes, K. Heydemann, N. Drach, P. Antoniu, A. Cohen : “Aftermath: Performance analysis of task-parallel applications on many-core NUMA systems”, Tenth International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems, Fiuggi, Italy (2014)

- A. Drebes, A. Pop, K. Heydemann, A. Cohen, N. Drach : “Aftermath: A graphical tool for performance analysis and debugging of fine-grained task-parallel programs and run-time systems”, Seventh Workshop on Programmability Issues for Heterogeneous Multicores (MULTIPROG-2014), Vienna, Austria (2014)

-

2012

- M. Rosière, J.‑L. Desbarbieux, N. Drach, F. Wajsbürt : “An Out-of-Order Superscalar Processor on FPGA: The ReOrder Buffer Design”, DATE Design Automation and Test in Europe Conference, Dresden, Germany, pp. 1549-1554, (IEEE) (2012)

-

2011

- M. Rosière, J.‑L. Desbarbieux, N. Drach, F. Wajsbürt : “MORPHEO: a high-performance processor generator for a FPGA implementation”, DASIP IEEE International Conference on Design and Architectures for Signal and Image Processing, Tampere, Finland, pp. 1-8, (IEEE) (2011)

- O. Gamoudi, N. Drach, K. Heydemann : “Using runtime activity to dynamically filter out inefficient data prefetches”, Euro-Par European Conference on Parallel computing, vol. 6852, Lecture Notes in Computer Science, Bordeaux, France, pp. 338-350, (Springer) (2011)

- M. Nguyen, B. Robisson, M. Agoyan, N. Drach : “Low-cost recovery for the code integrity protection in secure embedded processors”, Symposium on Hardware-Oriented Security and Trust (HOST 2011), San Diego, United States, pp. 99-104 (2011)

- B. Robisson, M. Agoyan, S. Bouquet, M. Nguyen, S. Le Henaff, P. Soquet, G. Phan, F. Wajsbürt, P. Bazargan‑Sabet, N. Drach : “Management of the security in smart secure devices”, SSI 2010 - Smart Systems Integration, Dresden, Germany, pp. 1-9 (2011)

-

2010

- M.‑H. Nguyen, B. Robisson, M. Agoyan, N. Drach : “Low-cost fault tolerance on the ALU in simple pipelined processors”, DDECS 2010 - 13th International Symposium on Design and Diagnostics of Electronic Circuits and Systems, Vienne, Austria, pp. 28-31, (IEEE) (2010)

- M. Daumas, N. Drach : “Architecture des ordinateurs”, vol. 29 (2), RSTI série TSI, (Hermes Science Publications), (ISBN: 978-2746229211) (2010)

-

2009

- M. Nguyen, B. Robisson, M. Agoyan, N. Drach : “Evaluation of the Time-Redundant Fault Tolerance on the ALU for Simple Pipelined Processor”, 4th Annual Austin Conference on Integrated Systems & Circuits, Austin, United States (2009)

- A. Djabelkhir, N. Drach, K. Heydemann, F. Arzel : “Parallélisation supervisée pour les multicoeurs embarqués”, SympA Symposium en Architecture de Machines, Toulouse, France (2009)

- O. Gamoudi, N. Drach, K. Heydemann : “Vers une méthode adaptative de préchargement de données”, SympA Symposium en Architecture de Machines, Toulouse, France (2009)

-

2008

- O. Certner, P. Palatin, Zh. Li, O. Temam, F. Arzel, N. Drach : “A Practical Approach for Reconciling High and Predictable Performance in Non-Regular Parallel Programs”, DATE Design Automation and Test in Europe Conference, Munich, Germany, pp. 740-745, (IEEE) (2008)

- O. Certner, Zh. Li, P. Palatin, O. Temam, F. Arzel, N. Drach : “A Practical Approach for Reconciling High and Predictable Performance in Non-Regular Parallel Programs”, MULTIPROG International Workshop on Programmability Issues for Multi-Core Computers, Göteberg, Sweden (2008)

- A. Coveliers, K. Heydemann, N. Drach : “Étude de la sensibilité aux jeux de données de la compilation itérative”, Revue des Sciences et Technologies de l'Information - Série TSI : Technique et Science Informatiques, vol. 27 (6), pp. 757-777, (Lavoisier) (2008)

-

2006

- A. Coveliers, K. Heydemann, N. Drach : “Sensibilité aux jeux de données de la compilation itérative”, SympA Symposium en Architecture de Machines, Perpignan, France, pp. 35-46 (2006)

-

2005

- C. Limousin, J. Sebot, A. Vartanian, N. Drach : “Architecture optimization for multimedia application exploiting data and thread-level parallelism”, Journal of Systems Architecture, vol. 51 (1), pp. 15-27, (Elsevier) (2005)

-

2004

- M. Dupré, N. Drach, O. Temam : “VHC: Quickly Building an Optimizer for Complex Embedded Architectures”, CGO IEEE/ACM International Symposium on Code Generation and Optimization, San Jose, California, United States, pp. 53-64, (IEEE) (2004)