# The Informatics of Time and Events

**Gérard Berry**

http://www-sop.inria.fr/members/Gerard.Berry/

Professor at Collège de France UPMC Colloquium, Paris, October 24<sup>th</sup>, 2012

## Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency models

- 5. Synchronous circuits and constructive logic

- 6. Metastability and inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

## Why Discussing Time and Events

- Real-Time Embedded Systems

- Systems of Chips (SoCs)

- Simulators of physical systems

- Orchestration of Web Services

- Music composition and interpretation

Dealing with time and events is a key issue, becoming much more important in the 21<sup>th</sup> century No provision in classical languages to handle them!

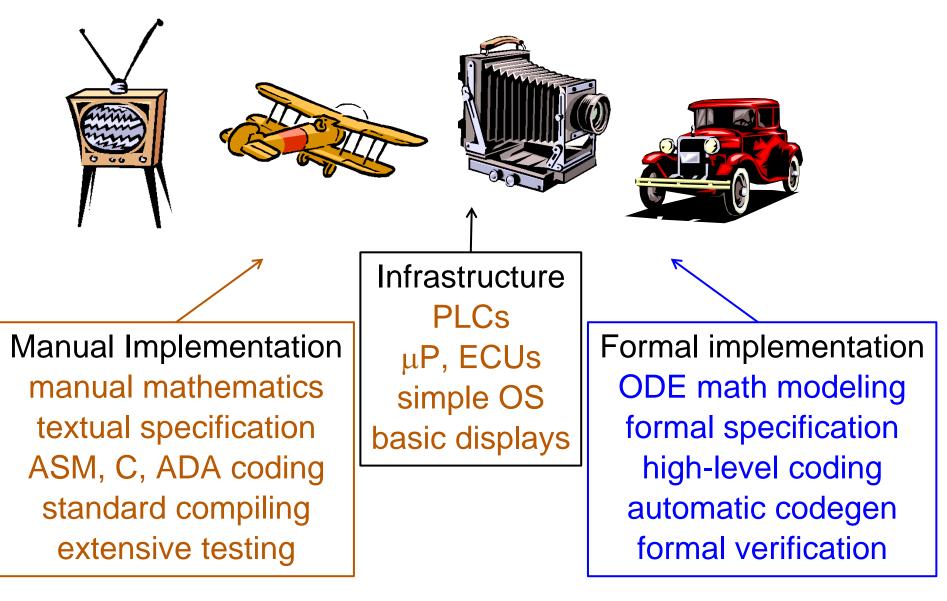

## 20<sup>th</sup> Century Embedded Systems

- Compact, single functionality

- data-centric: continuous control, signal processing

- control-centric: protocols, mode handlers, displays, etc.

- Mostly deterministic behavior

- time-based control-theory

- deterministic event handling, external-only non-determinism

### 20<sup>th</sup> Century Embedded Systems

# 21<sup>th</sup> Century Embedded Systems

- Much more complex, distributed, non-deterministic

- many functions on each SoC or ECU, many clocks

- subsystem functions need to be coordinated

- networks everywhere: NoCs, PAN, LAN, etc.

- Mix of styles

- distributed continuous control + FSMs

- GALS: Globally Asynchronous Locally Synchronous

- mathematical modeling: continuous + discrete time

- Web-based "best effort" interfaces

- -ex.: controlling the house from a smartphone

# 20<sup>th</sup> Century Chips

- Simple functionality

- Single clock

- Simple physics

- No power-handling

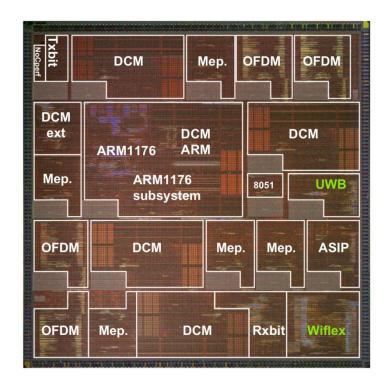

# 21<sup>th</sup> Century Chips

- Multiple IPs, multiple clock zones, complex power risks of metastability

complex communication protocols

- Need for multiple simulation levels build the software before the chip  $\Rightarrow$  TLM simulation

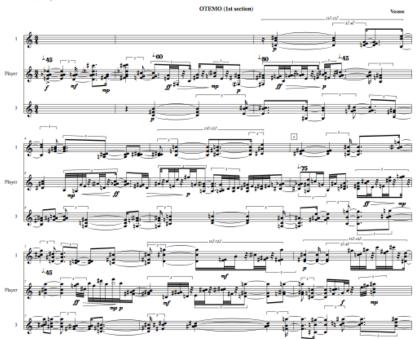

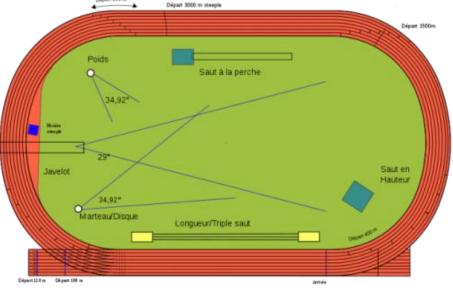

#### 20th Century : Human Music and Score

G. Berry, UPMC 24/10/2012 10

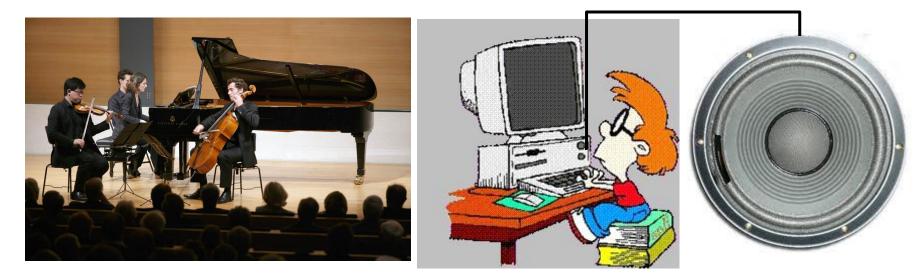

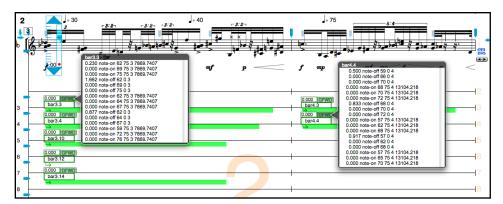

### 21<sup>st</sup> Century: Adaptive Human / Electronics

#### **Algorithmic Score**

G. Berry, UPMC 24/10/2012 11

## Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency models

- 5. Synchronous circuits and constructive logic

- 6. Metastability and inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

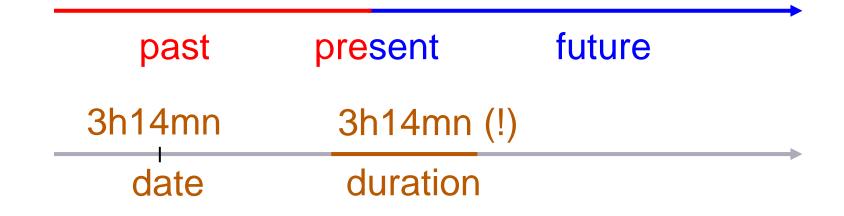

### The Line of Time

- present is an instant between past and future

- Strange date numbering: 01/01 at 0h00

In the past, there was more future than nowadays (le Chat)

#### Mathematical Continuous Time

G. Berry, UPMC 24/10/2012 14

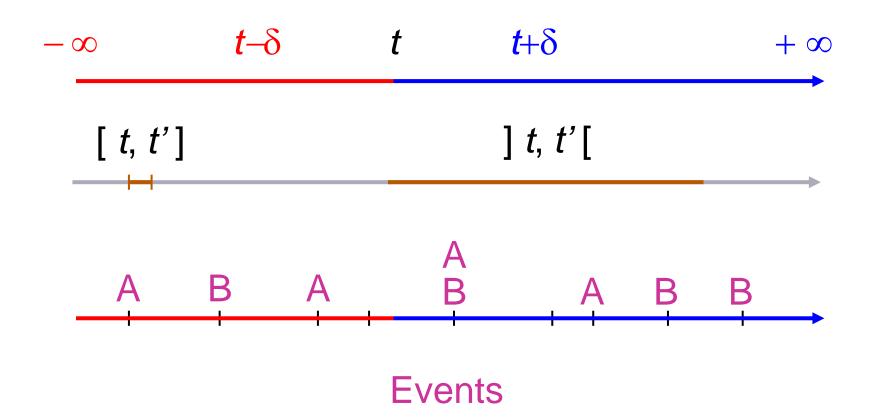

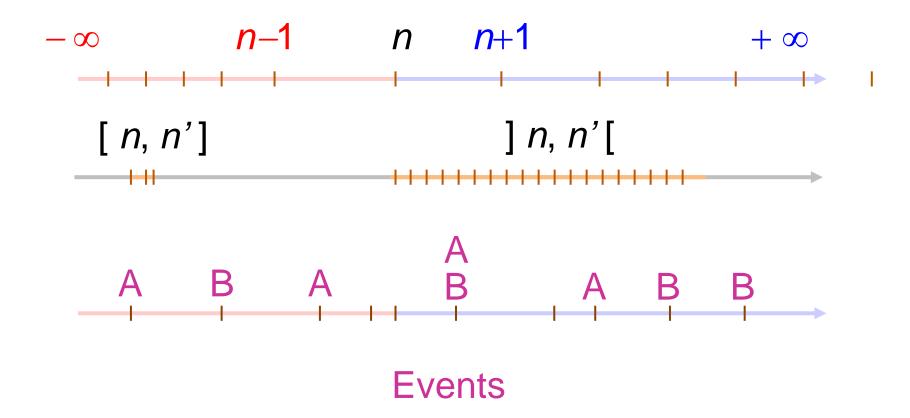

#### Mathematical Discrete Time

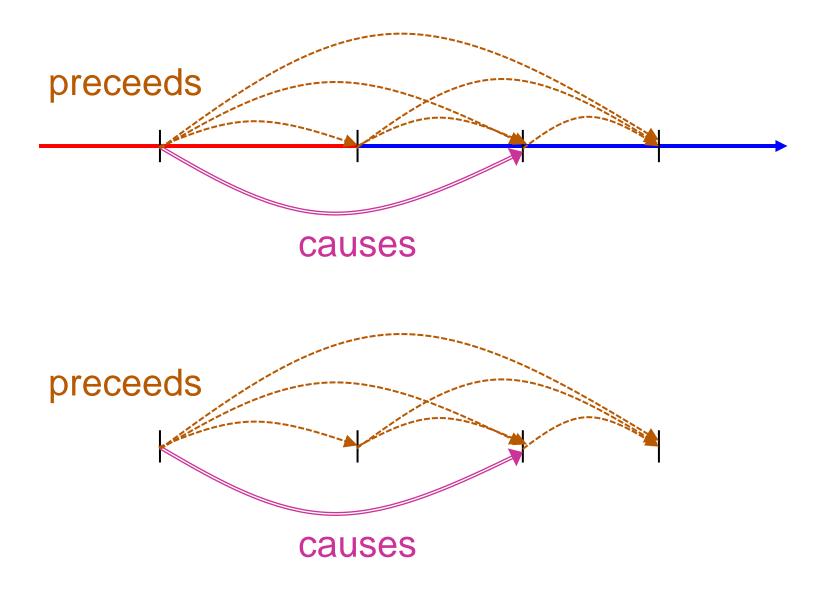

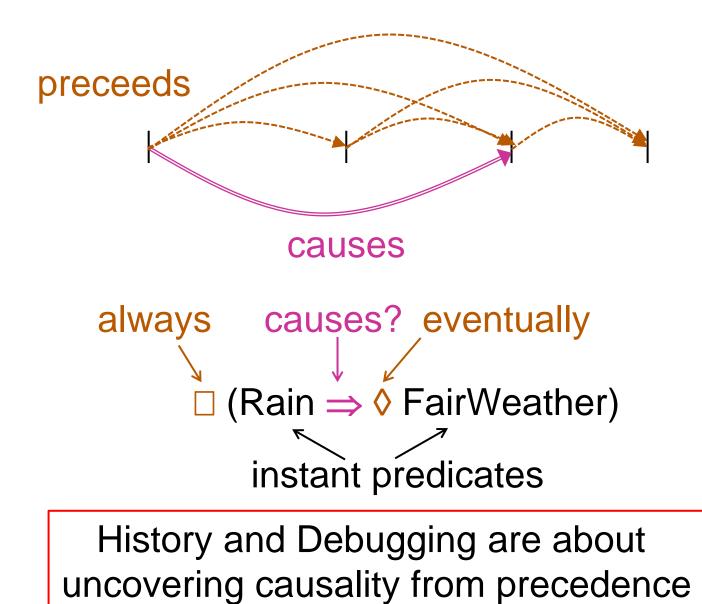

#### Precedence vs. Causality

## Linear Temporal Logic

G. Berry, UPMC 24/10/2012 17

# Is Time a Physical or Logical Concept?

- In physics, is time continuous or discrete?

- it depends on which physics !

- discrete is an approximation of continuous, and conversely !

- Do instants have a thickness?

l'espace d'un instant → Einstein

- Can we act in zero-time? – it depends on which physics !

- How do the times of different actors compare?

A looong history of time measurement / adjustment

- made much more complex by relativity theories: GPS

- Is linear time enough for reasoning about systems?

No, by far !

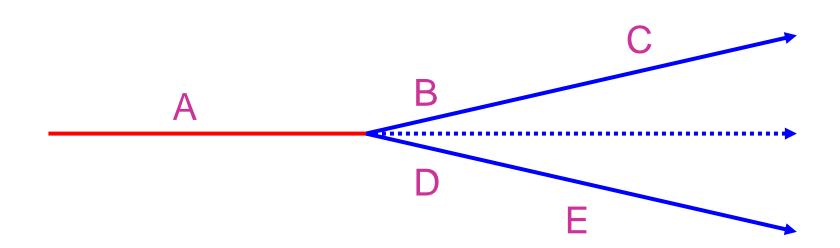

#### The Cone of Time

#### Knowing that I have done A: if I do B, I will get C but if I do D, I will get E

$\Rightarrow$  branching-time temporal logics

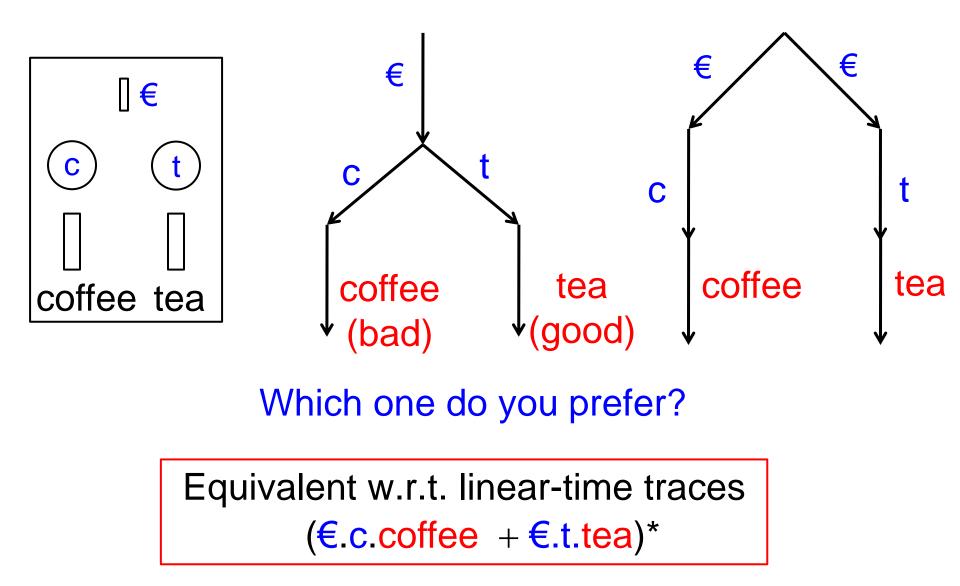

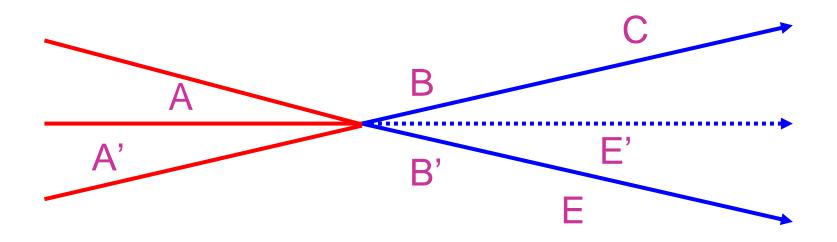

#### British vs. French Coffee Machine

#### British vs. French Coffee Machine

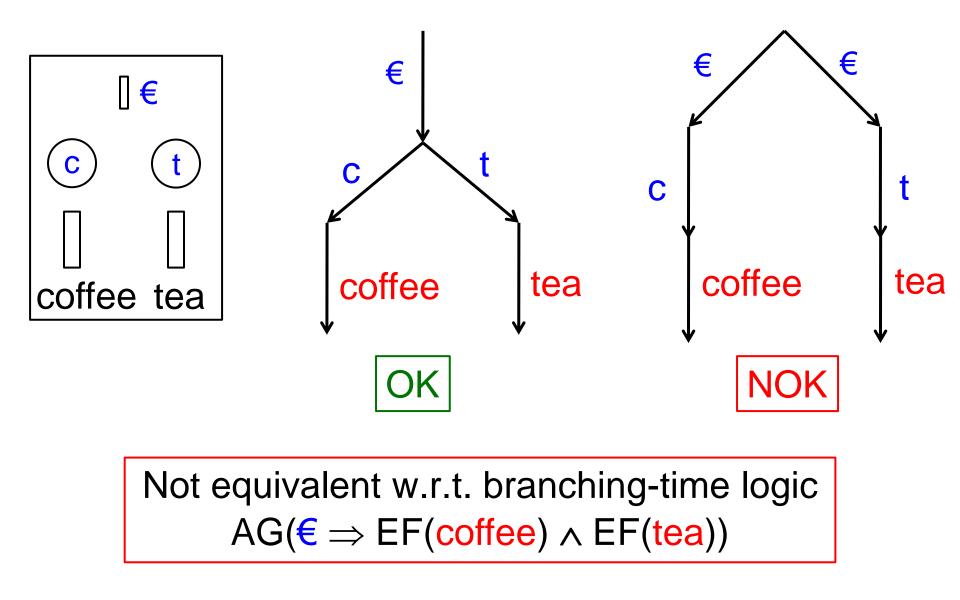

#### The Double Cone of Time

Had I known, A' would have been much better than A I would have got C without even doing B and, by doing B', I would have got E', better than E !

# Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency models

- 5. Circuits and constructive logic

- 6. Metastability, inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

## Multiform Time: Clock Hierarchies

Second  $\rightarrow$  Hour  $\rightarrow$  Morning Meter  $\rightarrow$  Lap Step HeartBeat  $\rightarrow$  HeartAttack

#### The Esterel Runner trap HeartAttack in every Morning do abort loop abort run Slowly when 100 Meter ; abort every Step do run Jump || run Breathe || CheckHeart end every when 15 Second ; exit HeartAttack run FullSpeed each Lap when 4 Lap end every handle HeartAttack fo run RushToHospital end trap

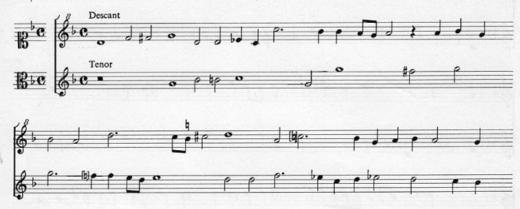

#### *Music* Score $\Rightarrow$ *Multiform Time*

Fantasie XXI: La Tortorella?

Urtext edition prepared by Roderick Biss

THOMAS MORLEY

#### Thomas Morley 1557-1602

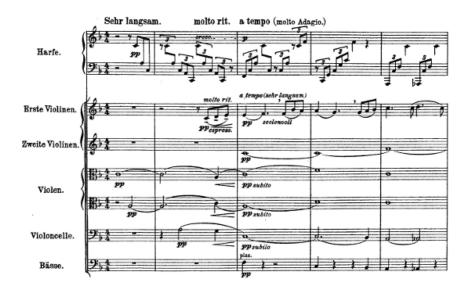

#### Gustav Mahler 1557-1602

# Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency models

- 5. Circuits and constructive logic

- 6. Metastability, inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

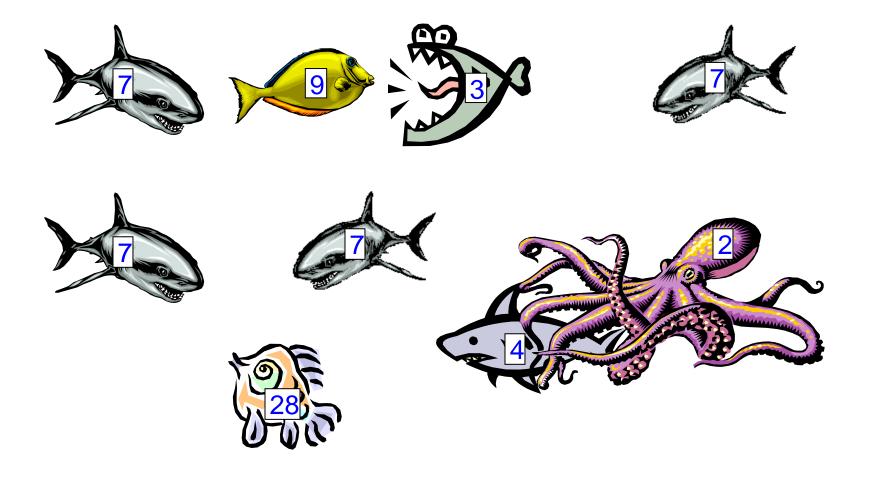

## The Asynchronous Darwin Sieve: $p, kp \rightarrow p$

#### CHAM : Internet, cellular biology, etc.

## The Synchrony / Vibration Model

#### Synchronous

Musicians and spectators neglect the speed of sound

#### Vibration

Acousticians deal with sound propagation

## The Synchrony / Vibration Model

If the room is small enough Vibration implements synchrony for spectators However, if the orchestra is big enough Musicians need light + conductor to synchronize

## Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency modes

- 5. Synchronous circuits and constructive logic

- 6. Metastability, inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

### Synchronous Circuits: Vibration View

Since the network is acyclic, outputs stabilize in bounded time if inputs are kept constant Stabilization time is determined by the critical path

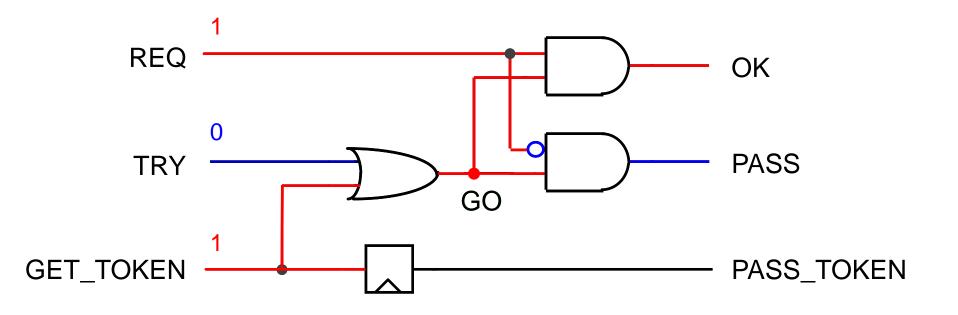

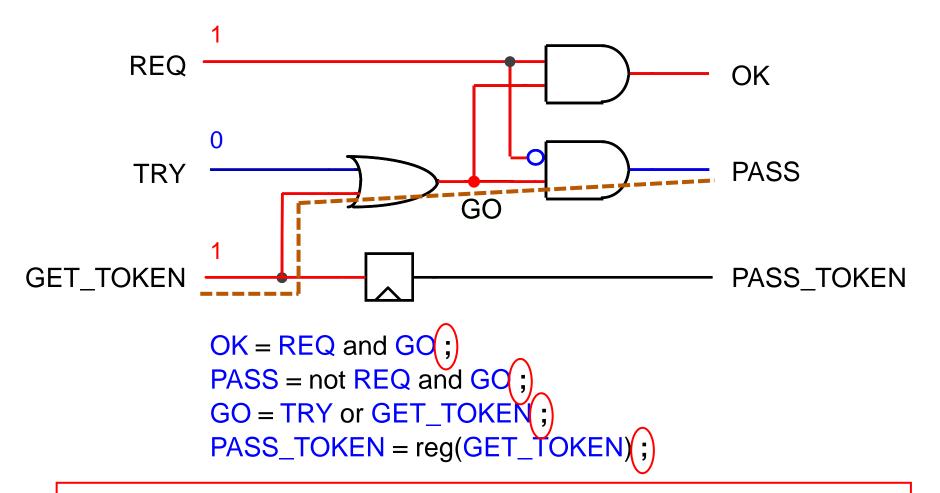

## Synchronous Circuits: Synchronous View

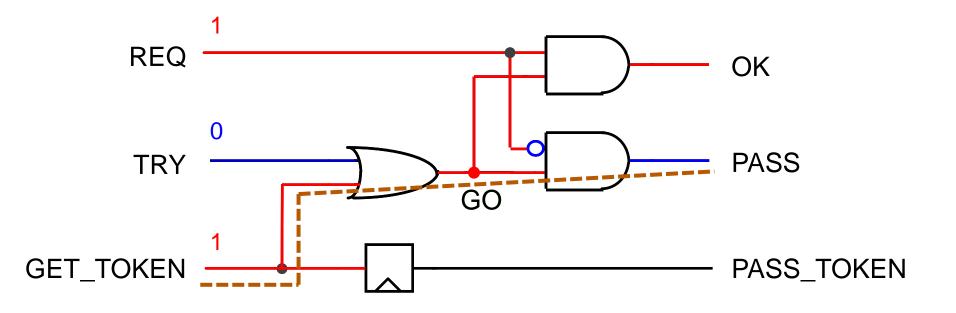

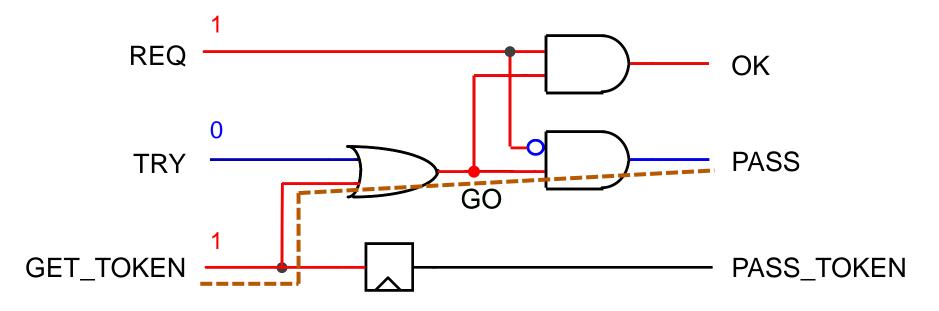

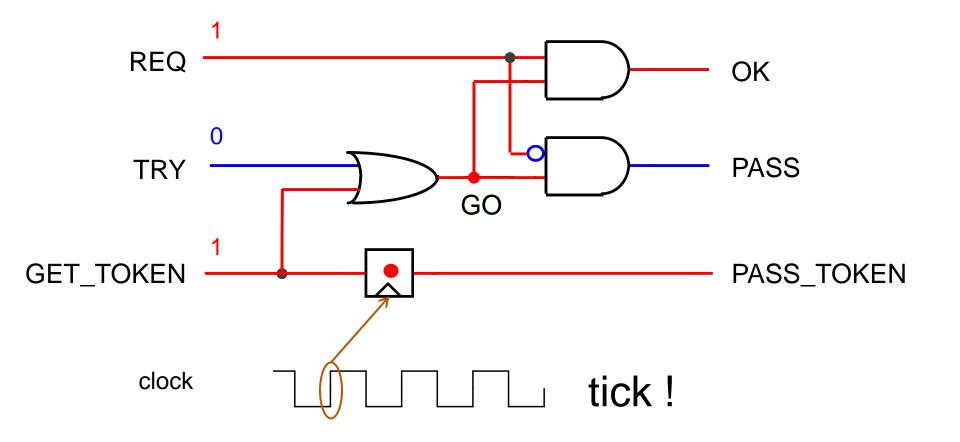

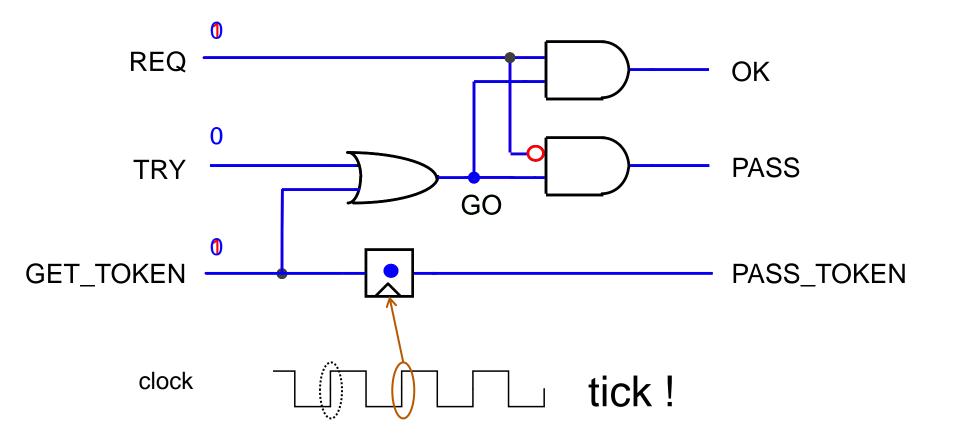

OK = REQ and GO PASS = not REQ and GO GO = TRY or GET\_TOKEN PASS\_TOKEN = reg(GET\_TOKEN)

Acyclic case:

waiting for the critical time  $\Leftrightarrow$  solving the equations

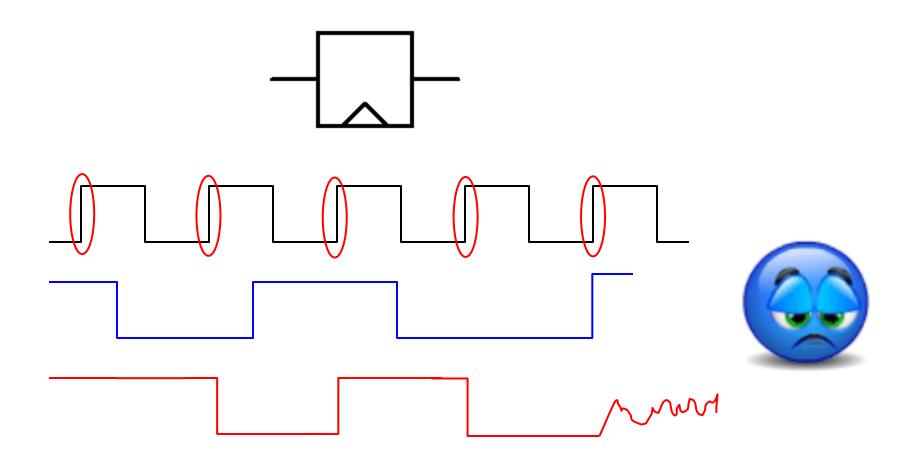

### Sequential sampling

### Sequential sampling

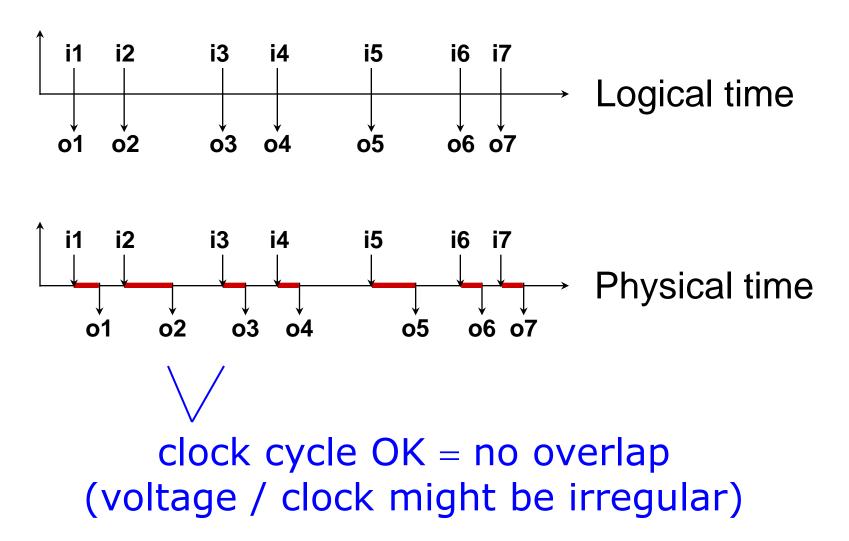

#### Logical Time vs. Physical Time

#### Combinational Circuit = Proof Network

#### Each operator is a proof component circuit = graph of all proofs of outputs from inputs

# **Constructive Boolean Propagation Logic**

- Input vector  $\mathcal{J} = \text{inputs} \rightarrow \{0, 1\}$

- Formulae:  $\mathcal{J} \vdash \mathbf{e} = \mathbf{b}$

*J* ⊢ e = 1  $\mathcal{J} \vdash \mathbf{e} = 0$  $\mathcal{J} \vdash I = \mathcal{J}(I)$   $\mathcal{J} \vdash not e = 1$   $\mathcal{J} \vdash not e = 0$  $\mathbf{J} \vdash \mathbf{e} = 1$   $\mathbf{J} \vdash \mathbf{e}' = 1$  $\mathcal{J} \vdash \mathbf{e} = 0$  $\mathbf{J} \vdash \mathbf{e}' = \mathbf{0}$  $\mathbf{J} \vdash \mathbf{e}$  and  $\mathbf{e}' = 0$   $\mathbf{J} \vdash \mathbf{e}$  and  $\mathbf{e}' = 0$   $\mathbf{J} \vdash \mathbf{e}$  and  $\mathbf{e}' = 1$  $\mathbf{J} \vdash \mathbf{e} = 1$   $\mathbf{J} \vdash \mathbf{e}' = 1$   $\mathbf{J} \vdash \mathbf{e} = 0$   $\mathbf{J} \vdash \mathbf{e}' = 0$  $\mathcal{J} \vdash \mathbf{e} \text{ or } \mathbf{e}' = 1$   $\mathcal{J} \vdash \mathbf{e} \text{ or } \mathbf{e}' = 1$   $\mathcal{J} \vdash \mathbf{e} \text{ or } \mathbf{e}' = 0$ X = e  $\mathcal{J} \vdash e = b$  $\mathcal{J} \vdash X = b$

### Constructive = No Excluded Middle !

$$\mathcal{J} \vdash \mathbf{e} \text{ or not } \mathbf{e} = 1$$

iff  $\mathcal{J} \vdash \mathbf{e} = 0$  or  $\mathcal{J} \vdash \mathbf{e} = 1$

G. Berry, UPMC 24/10/2012 43

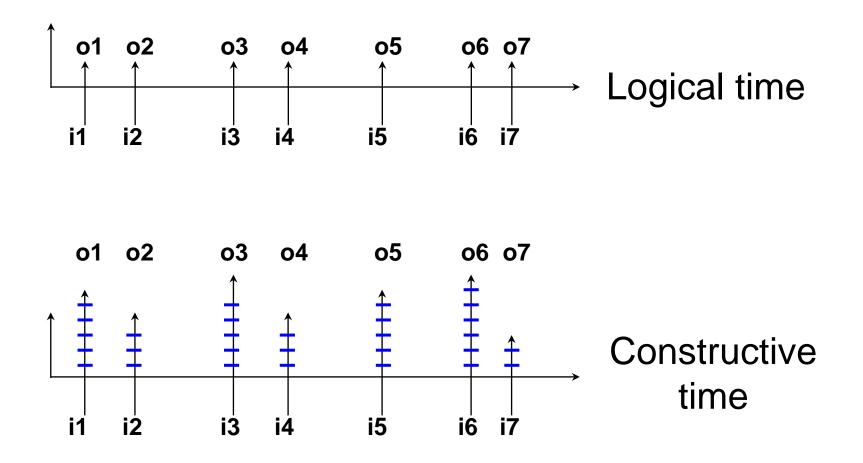

## Logical Time vs. Constructive Time

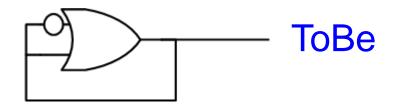

# **Dubious Circuits**

### Hamlet : ToBe = ToBe or not ToBe

- Logically computes 1 in classical logic, but computes nothing in constructive logic

- Electrically stabilizes to 1 for some gate and wire delays, but not for all delays!

<u>Theorem</u> (Mendler-Shiple-Berry) :

constructive ⇔ electrically stable for all delays

# Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency modes

- 5. Synchronous circuits and constructive logic

- 6. Metastability and inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

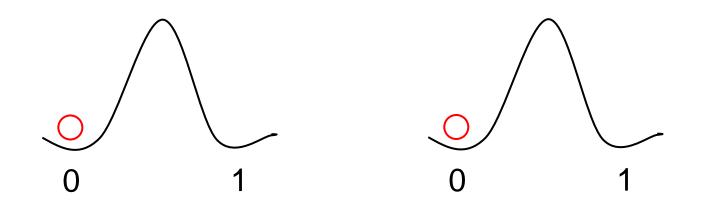

## Metastability

### The Ball on Hill Image

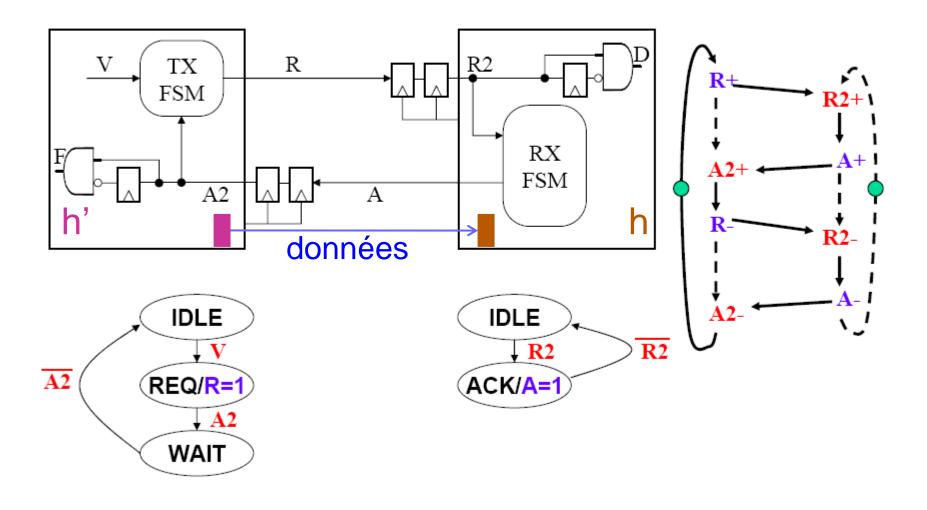

# The Four Phase Synchronizer

# Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency modes

- 5. Synchronous circuits and constructive logic

- 6. Metastability and inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

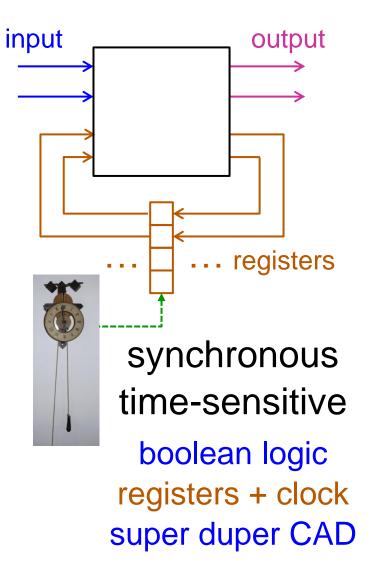

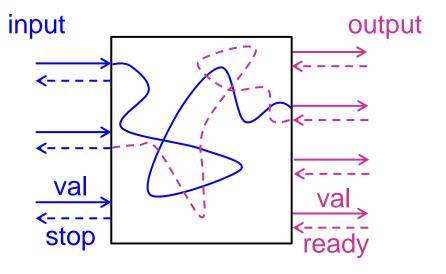

# Synchronous vs. Asynchronous Circuits

asynchronous time-insensitive

no clock, 2\*wires fancier logic difficult CAD

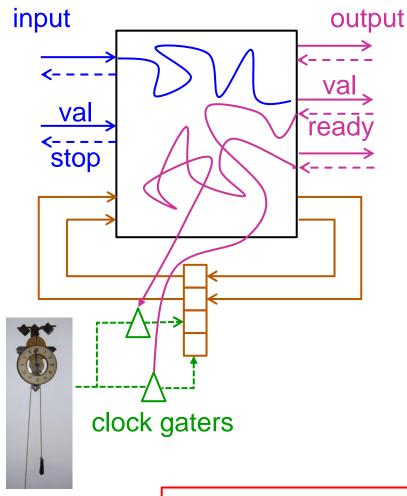

# Elastic Circuits

boolean logic + regs + clocks asynchronous logic + clock gaters

> synchronous CAD time-insensitive bubble-insensitive ⇒ cutting long lines OK

### J. Cortadella, M. Kishinevsky et.al.

# Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency modes

- 5. Synchronous circuits and constructive logic

- 6. Metastability and inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

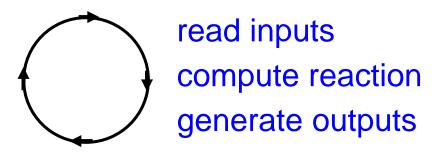

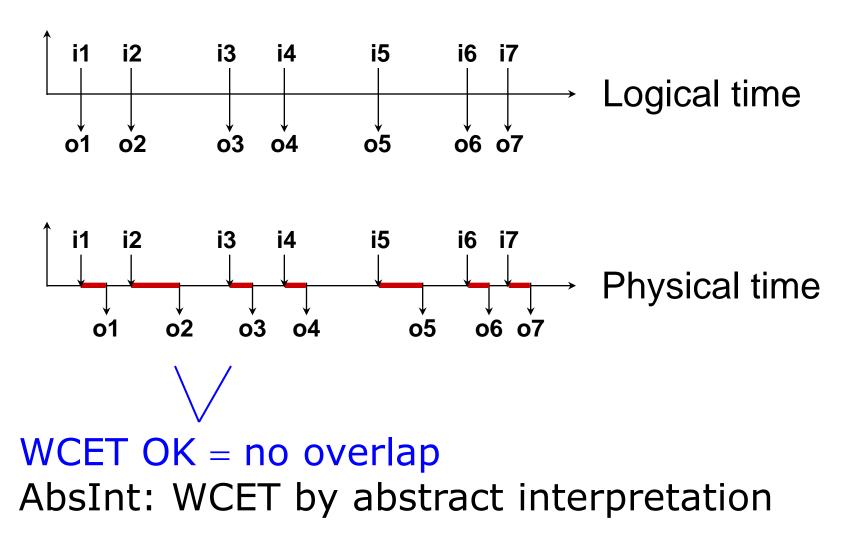

# Cycle-Based Software Synchrony

### Cyclic execution

Synchronous = Zero-delay = within the same cycle parallel propagation of control parallel propagation of signals

Interference freedom => determinism by construction Very elegant mathematics

# Synchronous Circuits: Simulation View

Sort equations to match electrical causal order with implementation-dependent sequential order

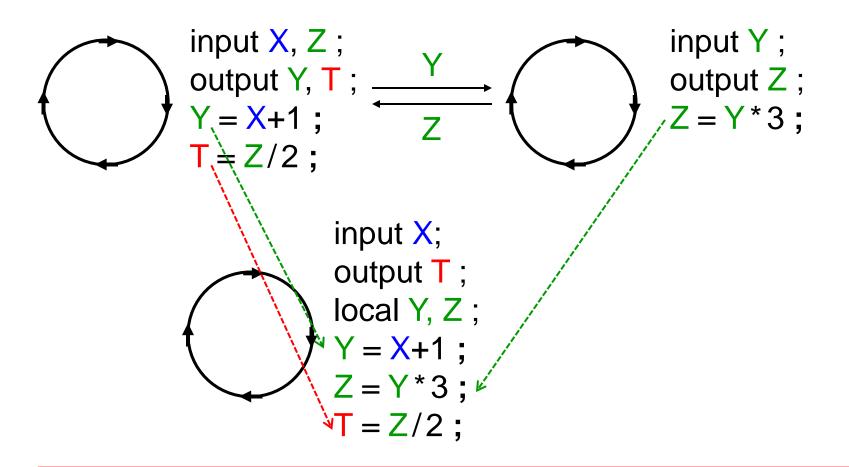

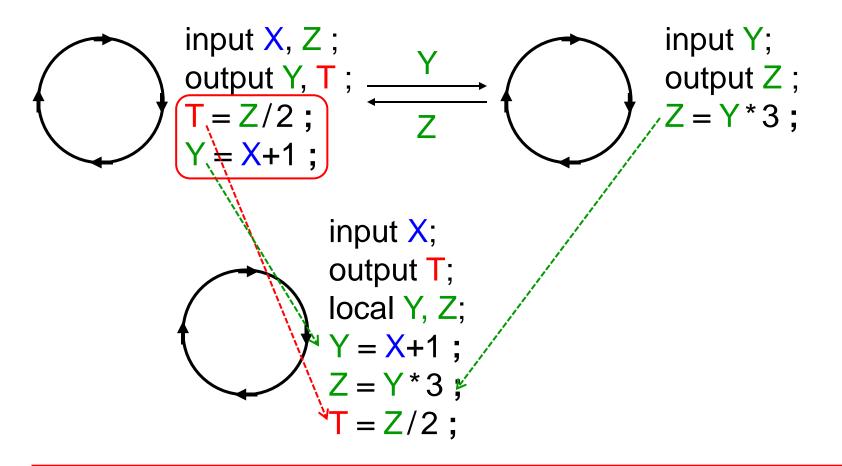

# Resolving Concurrency by Cycle Fusion

No synchronization, no deadlock, no context switch Room size control = Worst Case Execution Time

### Beware of causal vs. implementation order!

No block-level compositionality possible Sequential order should be slave of causal order

## Logical Time vs. Physical Time

## Lustre = Synchronous Data Flow

#### EventCounter

Event = false true false true false true false true false true false false true true falseCount = 0112333455

$$\begin{cases} Count(0) = 0 \\ \forall t > 0, \ Count(t) = \begin{cases} Count(t-1) + 1, & \text{if } Event(t) = true \\ Count(t-1), & otherwise \end{cases}$$

$\begin{array}{l} \text{Count} = 0 \rightarrow (\text{if Event} \\ \text{then pre(Count)+1} \\ \text{else pre(Count)}) \\ \text{Event} = \text{false} \rightarrow \text{not}(\text{pre(Event)}) \end{array}$

Textual Lustre

#### SCADE Block Diagram

G. Berry, UPMC 24/10/2012 71

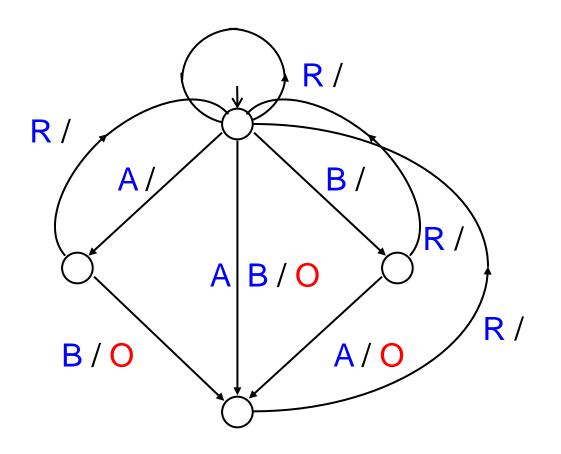

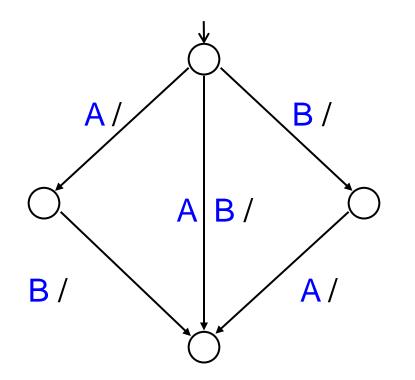

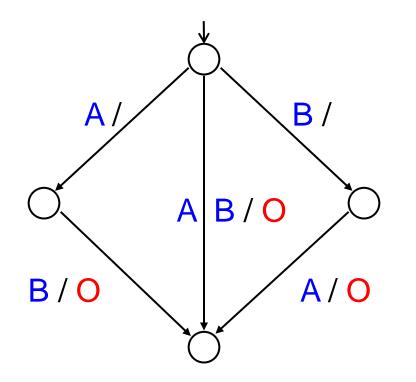

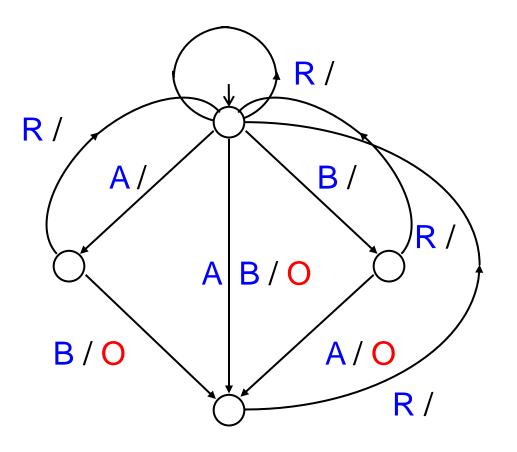

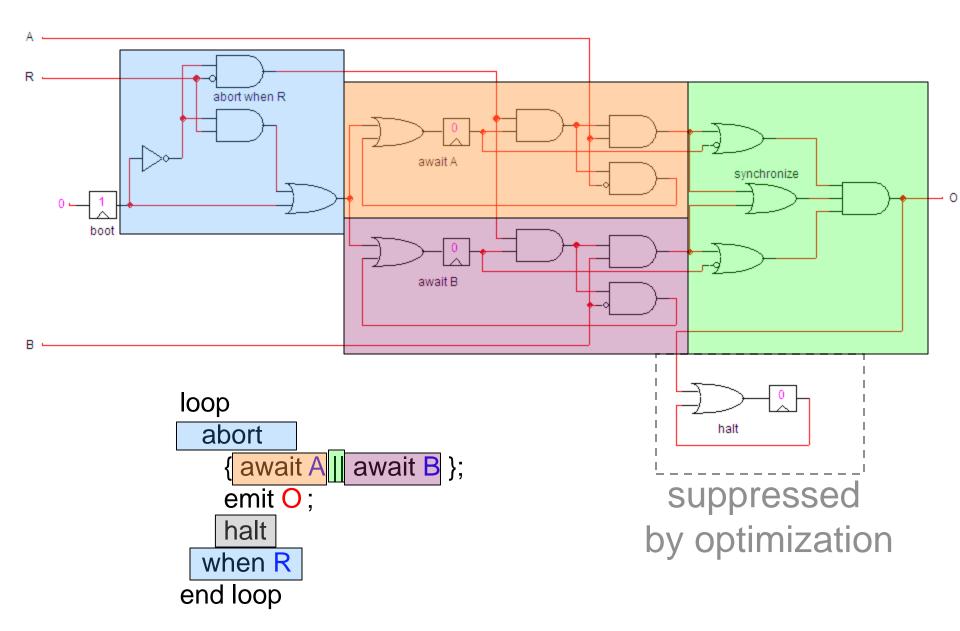

# The ABRO Synchronization Example

Emit O as soon A and B have arrived Reset this behavior each R

Memory Write

- R : request

- A : address

- B: data

- O: write

### Esterel = Linear Specification

### { await A || await B }; halt

### Esterel = Linear Specification

{ await A || await B }; emit O; halt

### Esterel = Linear Specification

loop abort { await A || await B }; emit O; halt when R end loop

# The ABRO Circuit (Proof Network)

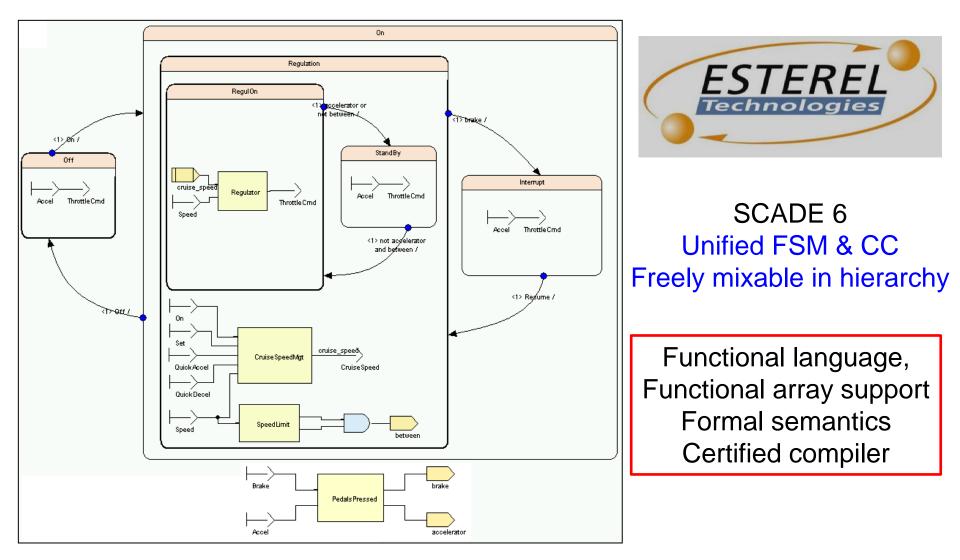

# Scade 6 for Certified Avionics = CC+FSM

See also Ptolemy II, Ed Lee, UC Berkeley

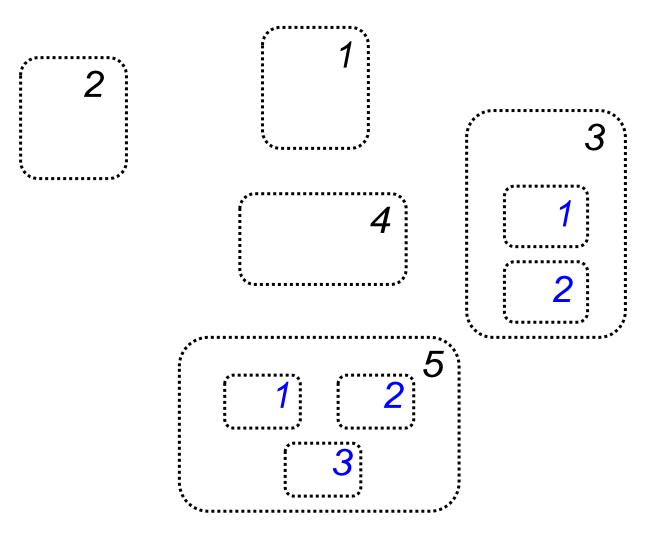

# Bad: Scheduling by Physical Position !

#### Initial choice : block-level parallelism

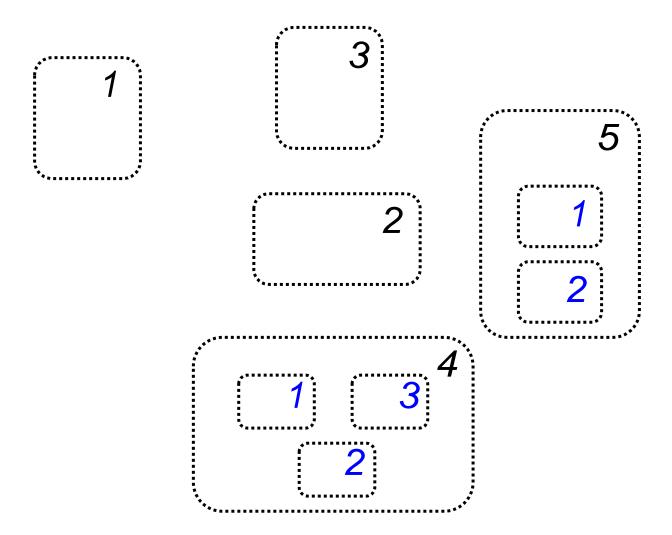

# Bad : Scheduling by Creation Order !!

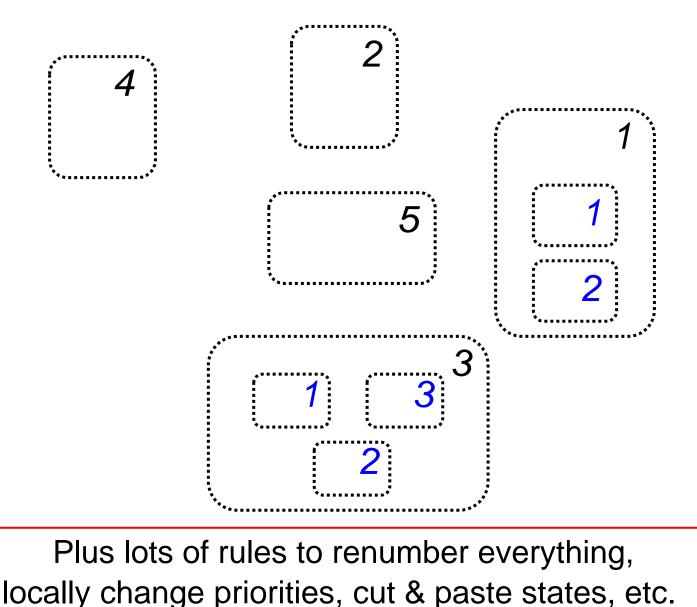

# Complicated: Manual Rescheduling !!!

• Pollution: block-level sequential code generation makes causal dependencies depend on implementation ones

Why are parallel priorities needed at all? Parallelism should be associative, commutative, and modular!

Semantics and compiler handle parallelism, not users! Cf. Lustre, Esterel, SyncCharts, SCADE 6, Ptolemy II,...

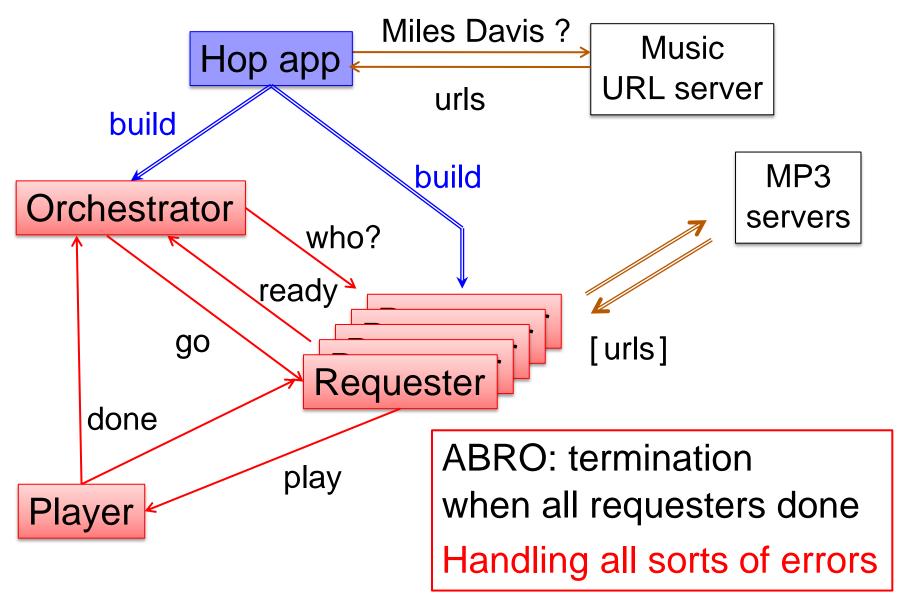

# Hop + HipHop : A Web Dynamic Esterel

# Agenda

- 1. Why discussing time and events

- 2. Lines and cones of time, causality

- 3. Multiform time

- 4. Concurrency modes

- 5. Synchronous circuits and constructive logic

- 6. Metastability and inter-clock zone protocols

- 7. Asynchronous and elastic circuits

- 8. Synchronous languages

- 9. Continuous vs. discrete time in modelers

10.Conclusion

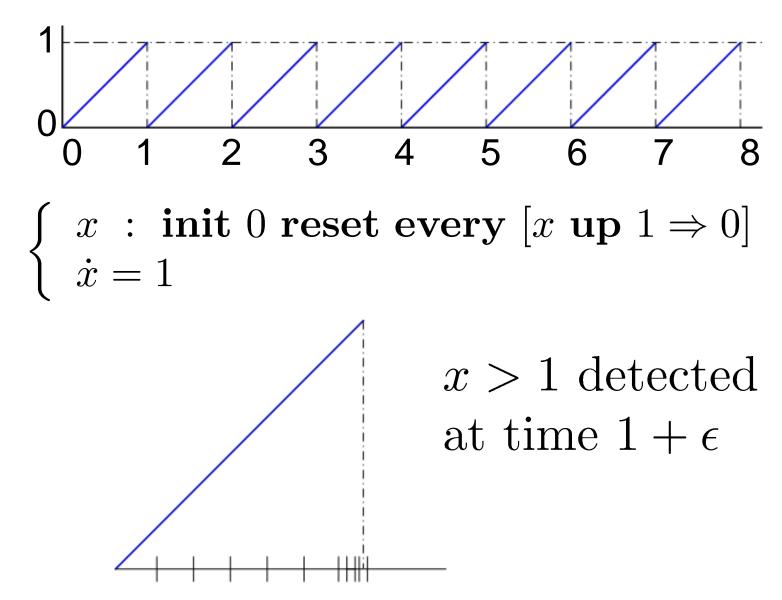

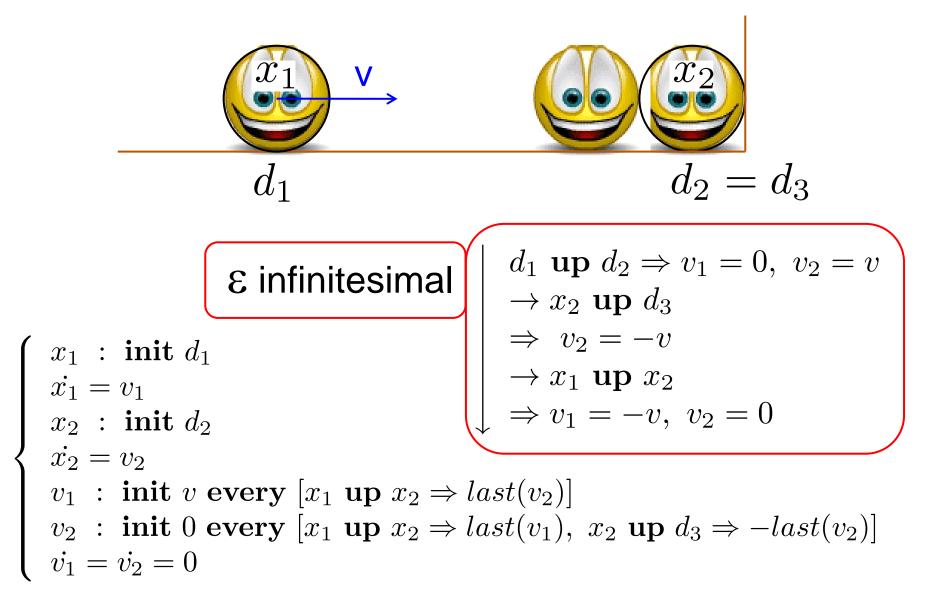

# *Hybrid Modeling : ODE + mode transitions*

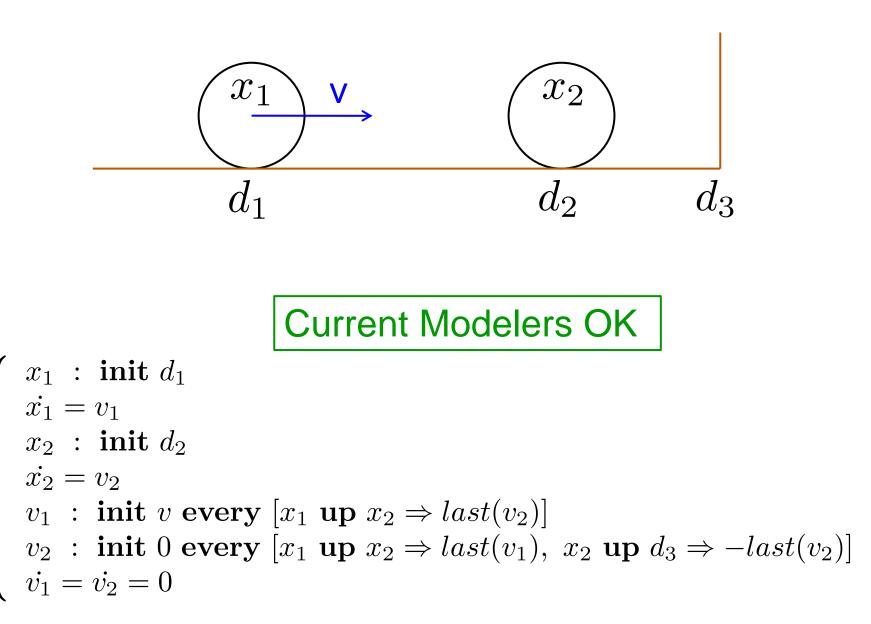

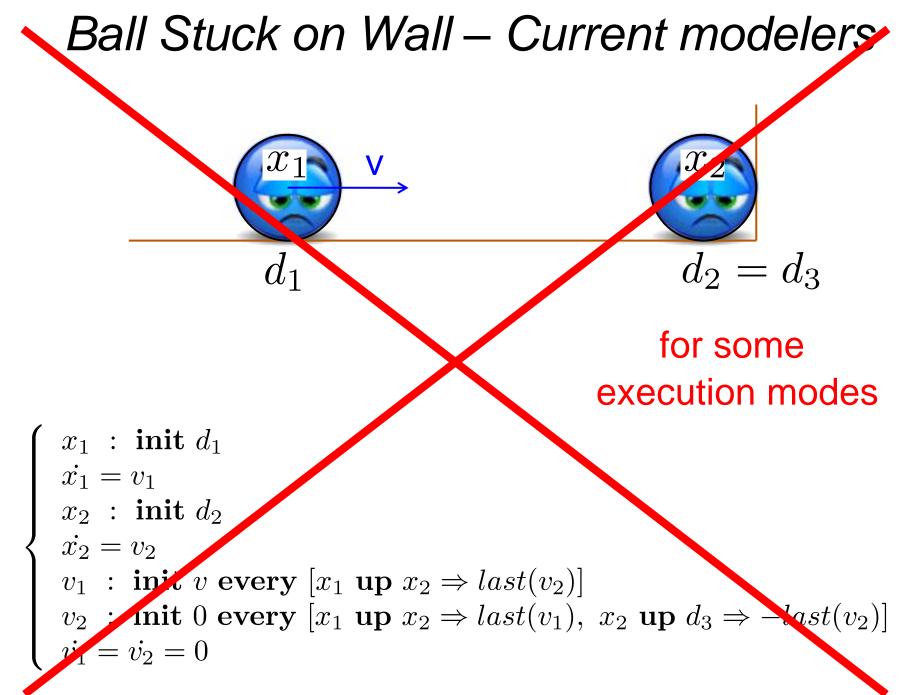

### Balls on Wall

G. Berry, UPMC 24/10/2012 91

## Non-Standard Constructive Analysis

# Conclusion

- There are two opposite ways to build systems

- hack them, test them, and hope they work

- think about them, and use well-defined tools

- Synchronous languages form a very strong basis

- with constructive semantics as a basic principle

- with extensive industrial development

- Their constructive semantics principle extend well

- to GALS systems (known)

- to continuous / discrete time modeling new

- to web-based control new

- to sound synthesis and music composition new